VREDUCEPH - REDUCE Packed Half

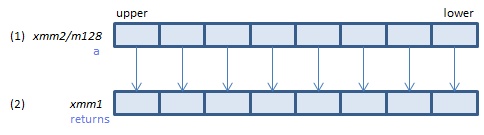

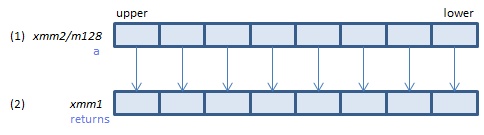

VREDUCEPH xmm1{k1}{z}, xmm2/m128/m16bcst, imm8 (V5+FP16+VL

__m128h _mm_reduce_ph(__m128h a, int imm8)

__m128h _mm_mask_reduce_ph(__m128h s, __mmask8 k, __m128h a, int imm8)

__m128h _mm_maskz_reduce_ph(__mmask8 k, __m128h a, int imm8)

For each FP16, round (1) to n-bit below the decimal point, subtract the result from (1), and store the remainder in (2).

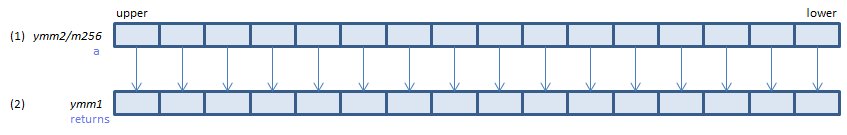

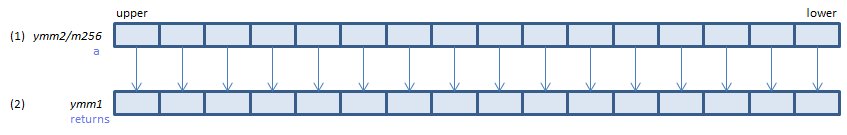

VREDUCEPH ymm1{k1}{z}, ymm2/m256/m16bcst, imm8 (V5+FP16+VL

__m256h _mm256_reduce_ph(__m256h a, int imm8)

__m256h _mm256_mask_reduce_ph(__m256h s, __mmask16 k, __m256h a, int imm8)

__m256h _mm256_maskz_reduce_ph(__mmask16 k, __m256h a, int imm8)

For each FP16, round (1) to n-bit below the decimal point, subtract the result from (1), and store the remainder in (2).

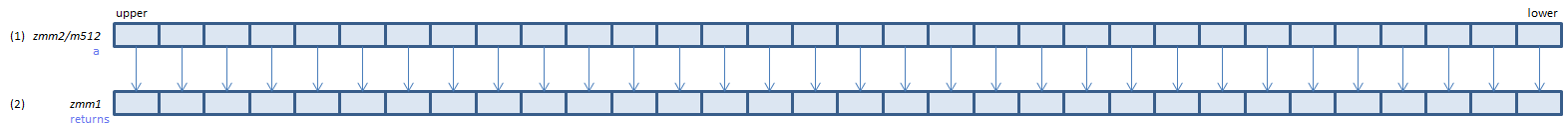

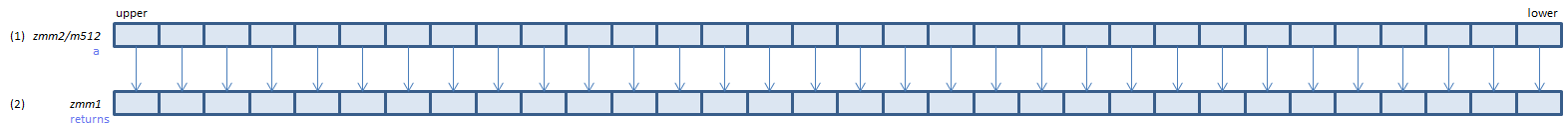

VREDUCEPH zmm1{k1}{z}, zmm2/m512/m16bcst{sae}, imm8 (V5+FP16

__m512h _mm512_reduce_ph(__m512h a, int imm8)

__m512h _mm512_mask_reduce_ph(__m512h s, __mmask32 k, __m512h a, int imm8)

__m512h _mm512_maskz_reduce_ph(__mmask32 k, __m512h a, int imm8)

__m512h _mm512_reduce_round_ph(__m512h a, int imm8, int sae)

__m512h _mm512_mask_reduce_round_ph(__m512h s, __mmask32 k, __m512h a, int imm8, int sae)

__m512h _mm512_maskz_reduce_round_ph(__mmask32 k, __m512h a, int imm8, int sae)

For each FP16, round (1) to n-bit below the decimal point, subtract the result from (1), and store the remainder in (2).

imm8

| bit |

|

| 7:4 |

Bits to preserve below decimal point (0 to 15).

Set 0 in this field to round to decimal point (like ROUNDPD / ROUNDPS).

|

| 3 |

0: precision exception mask is specified by MXCSR

1: precision exception is masked

|

| 2 |

0: rounding mode is specified by bit 1:0

1: rounding mode is specified by MXCSR

|

| 1:0 |

00: round to nearest or even

01: round toward negative infinity

10: round toward positive inifinity

11: round toward zero

|

x86/x64 SIMD Instruction List

Feedback